Ivy Bridge CPUs in x20-Serie: Unterschied zwischen den Versionen

Keine Bearbeitungszusammenfassung |

|||

| (6 dazwischenliegende Versionen desselben Benutzers werden nicht angezeigt) | |||

| Zeile 1: | Zeile 1: | ||

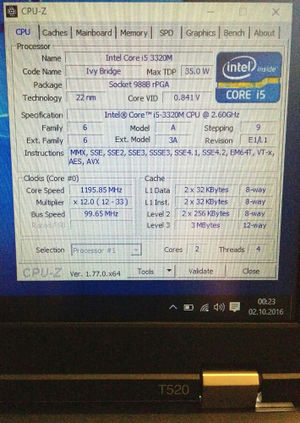

[[Datei:T520IvyBridge.jpg|mini|rechts|T520 mit i5-3320M]] | |||

== Motivation == | == Motivation == | ||

Neben einem moderaten Geschwindigkeitszuwachs und kühlerem Betrieb ist vor allem der Sprung von einer HD3000 auf eine HD4000-Grafik lohnenswert. | Neben einem moderaten Geschwindigkeitszuwachs und kühlerem Betrieb ist vor allem der Sprung von einer HD3000 auf eine HD4000-Grafik lohnenswert. | ||

| Zeile 16: | Zeile 18: | ||

Coreboot biete von Haus aus die Möglichkeit, beliebige Microcodes und ein VGA-Bios einzubinden. Die Initalisierung der Grafik erfolgt mit Hilfe der PCI ID. | Coreboot biete von Haus aus die Möglichkeit, beliebige Microcodes und ein VGA-Bios einzubinden. Die Initalisierung der Grafik erfolgt mit Hilfe der PCI ID. | ||

==== Anleitung | ==== Anleitung (in Arbeit) ==== | ||

Diese Anleitung orientiert sich weitgehend am [https://www.coreboot.org/Intel_Sandybridge_Build_Tutorial Coreboot Wiki], enthält aber die nötigen zusätzlichen Schritte für Ivy Bridge CPUs. | |||

1. Vorbereitungen | |||

* '''Host''': Um Coreboot zu bauen eignet sich am besten ein Linux-System mit einfacher Paketverwaltung (Debian o.ä.) | |||

* '''Hardwareflasher''': Dieser muss SPI auf 3.3V-Pegel sprechen. Ein Raspberry PI ist z.B. gut geeignet und kann anschließend auch anderweitig sinnvoll eingesetzt werden. | |||

* '''SOIC-Klammer''' oder '''Lackdraht''': Den Flash gibt es in verschiedenen Gehäuseformen, am einfachste ist es mit SOIC-8 - hier gibt es Klammern, die ohne zu Löten einfach huckepack aufgesetzt werden. Andere Gehäuseformen müssen ggfs. per Lackdraht kontaktiert werden. Meistens sind mehrere Footprints vorhanden, so dass sich beim regelmäßigen flashen das Aufbringen eines identischen ICs im SOIC-8 Package lohnt. | |||

* ggfs. '''3.3V Stromquelle''': Da zusätzlich zum Flash noch weitere Teile des Mainboards mit Spannung versorgt werden, reichen die 3.3V vom Programmer u.U. nicht aus und man muss extern einspeisen. | |||

== Status == | == Status == | ||

| Zeile 23: | Zeile 34: | ||

! Thinkpad !! Bios !! CPU !! OS!! Probleme | ! Thinkpad !! Bios !! CPU !! OS!! Probleme | ||

|- | |- | ||

| T520 (4241-RZ8) || Coreboot (Seabios) || i5-3320m || Windows 7/10, Xubuntu 16.04 || Akku-Kapazität wird falsch berechnet (Faktor 1.08) | | T520 (4241-RZ8) || Coreboot (Seabios) || style="background: green;" | i5-3320m || Windows 7/10, Xubuntu 16.04 || Akku-Kapazität wird falsch berechnet (Faktor 1.08) | ||

|- | |||

| || || style="background: yellow;" | i5-3320m || || | |||

|- | |||

| T420 (4180-AL1) || Coreboot (Seabios) || style="background: yellow;" | i3-3110m || tbd || Test steht noch aus | |||

|- | |||

| || || style="background: yellow;" | i5-3320m || || | |||

|} | |} | ||

== Benchmarks == | == Benchmarks == | ||

Aktuelle Version vom 10. Oktober 2016, 11:29 Uhr

Motivation

Neben einem moderaten Geschwindigkeitszuwachs und kühlerem Betrieb ist vor allem der Sprung von einer HD3000 auf eine HD4000-Grafik lohnenswert.

Methode

Sandy Bridge und Ivy Bridge-CPUs sind elektrisch kompatibel und es ist prinzipiell möglich, mit einem entsprechend ausgestatteten Chipsatz beide CPU-Generationen zu betreiben. Die Geräte der x20er-Generation (X220, T420, T520) wurden nur mit Sandy Bridge-CPUs ausgeliefert und eine Ivy Bridge-Unterstützung ist seitens des Lenovo-BIOS nicht gegeben. Da der Chipsatz aber grundsätzlich Kompatibilität bietet, kann diese Limitierung mit einem neuen oder modifizierten BIOS umgangen werden.

Lenovo-Bios

Um dem Lenovo-BIOS den Betrieb von Ivy Bridge CPUs zu ermöglichen, sind drei Dinge nötig:

- Neue Microcodes

- Neues VGA-BIOS

- VGA-Weiche zur Unterscheidung von HD3000/HD4000 und Initalisierung derselben

Die Entwicklung hängt zur Zeit an Punkt 3.

Coreboot

Coreboot biete von Haus aus die Möglichkeit, beliebige Microcodes und ein VGA-Bios einzubinden. Die Initalisierung der Grafik erfolgt mit Hilfe der PCI ID.

Anleitung (in Arbeit)

Diese Anleitung orientiert sich weitgehend am Coreboot Wiki, enthält aber die nötigen zusätzlichen Schritte für Ivy Bridge CPUs.

1. Vorbereitungen

- Host: Um Coreboot zu bauen eignet sich am besten ein Linux-System mit einfacher Paketverwaltung (Debian o.ä.)

- Hardwareflasher: Dieser muss SPI auf 3.3V-Pegel sprechen. Ein Raspberry PI ist z.B. gut geeignet und kann anschließend auch anderweitig sinnvoll eingesetzt werden.

- SOIC-Klammer oder Lackdraht: Den Flash gibt es in verschiedenen Gehäuseformen, am einfachste ist es mit SOIC-8 - hier gibt es Klammern, die ohne zu Löten einfach huckepack aufgesetzt werden. Andere Gehäuseformen müssen ggfs. per Lackdraht kontaktiert werden. Meistens sind mehrere Footprints vorhanden, so dass sich beim regelmäßigen flashen das Aufbringen eines identischen ICs im SOIC-8 Package lohnt.

- ggfs. 3.3V Stromquelle: Da zusätzlich zum Flash noch weitere Teile des Mainboards mit Spannung versorgt werden, reichen die 3.3V vom Programmer u.U. nicht aus und man muss extern einspeisen.

Status

| Thinkpad | Bios | CPU | OS | Probleme |

|---|---|---|---|---|

| T520 (4241-RZ8) | Coreboot (Seabios) | i5-3320m | Windows 7/10, Xubuntu 16.04 | Akku-Kapazität wird falsch berechnet (Faktor 1.08) |

| i5-3320m | ||||

| T420 (4180-AL1) | Coreboot (Seabios) | i3-3110m | tbd | Test steht noch aus |

| i5-3320m |